# Keysight W6600A-Series LPDDR4 BGA Interposers

# Notices

#### © Keysight Technologies 2016

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### Manual Part Number

W6601-97000

Edition

First Edition, March 2016

Available in electronic format only

Keysight Technologies 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCU-MENT IS PROVIDED "AS IS," AND IS SUB-JECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CON-SEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFOR-MANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATE-RIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

#### **Technology Licenses**

The hard ware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

#### Safety Notices

# CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### In This Guide

This document provides installation information for the following Keysight products:

- W6601A LPDDR4 BGA Interposer, 200-ball, 2-wings

- U4208A 61-pin ZIF from left wing probe/cable (160 pin direct connect to LA)

- U4209A 61-pin ZIF from right wing probe/cable (160 pin direct connect to LA)

# Contents

In This Guide 3

#### 1 Introduction to W6600-Series Interposers

#### W6600A-Series LPDDR4 BGA Interposers - An Overview 8

Compatibility with Logic Analyzer Modules 8

#### W6601A LPDDR4 BGA Interposer, 200-ball, 2-wings 9

Software Configurations 9 W6601A Technical Features Summary 10 W6601A Riser 10

#### U4208A 61-pin ZIF Probe / Cable (for Left Wing) 11

#### U4209A 61-pin ZIF Probe / Cable (for Right Wing) 12

Hard ware and Software Requirements 13

#### Mechanical Considerations 15

W6601A Interposer Dimensions15W6601A Riser Dimensions16W6601A Keep-Out Volume16

#### 2 W6600A-Series Interposers and Riser Soldering Guidelines

Recommended Soldering Guidelines 21

Soldering Steps 22

Interposer Fabrication Notes 24

#### 3 Setting up the W6601A Interposer

W6601A Interposer Setup - Overview 26

Soldering the W6601A Interposer 27

Connecting the W6601A Interposer to U4208A and U4209A Probe Cables 28 W6601A Interposer Wings Pinout 29

Connecting the U4208A and U4209A Probe Cables to a U4164A Logic Analyzer 31

Logic Analyzer Channels to Signals Mapping 31 Signals not probed by the Logic Analyzer 33

#### 4 Setting Up the Logic Analyzer for W6600A-series Interposers

#### Before You Start 36

#### Load ing a Configuration File 37

To save a configuration file 37

#### 5 Characteristics, Regulatory, Safety and Storage Information

#### **Operating Characteristics** 40

#### Storage, Inspection, Baking, and Cleaning Guidelines 41

Guidelines for Shelf Life and Solder-ability of W6600A-series Interposers 41 Cleaning of W6600A-series Interposer Gold Fingers 41

#### Regulatory Notices 42

WEEE Compliance 42 China RoHS 42

Index

Keysight W6600A-series LPDDR4 BGA Interposers Installation Guide

# 1 Introduction to W6600–Series Interposers

W6600A-Series LPDDR4 BGA Interposers - An Overview / 8 W6601A LPDDR4 BGA Interposer, 200-ball, 2-wings / 9 U4208A 61-pin ZIF Probe / Cable (for Left Wing) / 11 U4209A 61-pin ZIF Probe / Cable (for Right Wing) / 12 Hardware and Software Requirements / 13 Mechanical Considerations / 15

This chapter introduces the hardware components that are needed for a W6600A-series LPDDR4 BGA interposer setup. It also lists the software requirements as well as describes the mechanical considerations such as various dimensions and KOV that you should know before you start setting up and using these interposers.

#### W6600A-Series LPDDR4 BGA Interposers - An Overview

The W6600A-series LPDDR4 BGA Interposers enable probing of 200-pin JEDEC standard footprint directly at the ball grid array using the Keysight U4164A logic analyzer. These interposers provide you:

- single touch probing of DQ signals

- higher data rate (greater than 3.2 Gb/s)

- smaller KOV

Using these interposers, you can capture LPDDR4 signals above 2.5Gb/s without double probe load.

A W6600A-series interposer interposes between the DRAM being probed and the PC board where the DRAM would normally be soldered. The interposer is designed to be soldered to the PCB footprint for the DRAM on top of either the LPDDR riser included with the W6600-series BGA interposer or an optional Grypper socket (not included with the interposer) or both. The DRAM being probed is then soldered to the top side of the interposer.

Each DRAM signal in the common footprint passes directly from the bottom side of the interposer to the top side of the interposer.

Currently, in this series, Keysight provides the following interposer:

• W6601A LPDDR4 BGA Interposer, 200-ball, 2-wings

Compatibility with Logic Analyzer Modules

The W6600-series interposers are compatible with the Keysight U4164A AXIe-based logic analyzer module.

NOTE

All W6600A-series interposers are tested for via connections through the interposer and signal trace connectivity to the wing connections.

#### W6601A LPDDR4 BGA Interposer, 200-ball, 2-wings

The W6601A interposer has two flexible wings, each with a set of fingers for Zero Insertion Force (ZIF) connections that connect it to a U4208A or a U4209A 61-pin ZIF probe/cable. For the left wing of the interposer, you use the U4208A probe/cable and for the right wing of the interposer, you use the U4209A probe/cable. These cables are then connected to the U4164A Logic Analyzer module's pods.

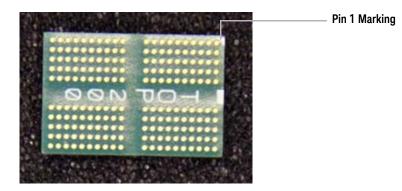

The following figure shows a W6601A interposer's top view.

| Pin 1 Marking 📃                       |            |                   |  |

|---------------------------------------|------------|-------------------|--|

|                                       |            |                   |  |

|                                       |            | P1 •              |  |

|                                       | P2         | LPDDR4<br>BGA 200 |  |

|                                       | Constant P | BGA 200           |  |

|                                       |            |                   |  |

| ? Flex wings with<br>/IF connectors – |            |                   |  |

#### Figure 1 W6601A Interposer

The W6601A interposer supports dual bank 16-bit data LPDDR4 200 ball DRAM that is being used as a single 32-bit channel device. The interposer probes a subset of the DQ data lines of both banks of such an LPDDR4 BGA 200 DRAM.

# If the DRAM is used as two single x16 channel devices, then the W6601A interposer can probe only CA signals from channel A.

This interposer is optimized to work with the U4164A logic Analyzer module to achieve higher data rates with smaller KOV.

#### Software Configurations

NOTE

The W6601A interposer can be used in the following three logic analyzer software configurations:

- 10 GHz Timing mode

- State mode under 2500 Mb/s (double edge clocking)

- State mode over 2500 Mb/s (single edge clocking)

This interposer effectively utilizes the single touch probing and quad sampling features of the U4164A logic analyzer module thereby allowing you to probe LPDDR4 DQ signals above 2.5Gb/s without double probe load. (In quad sampling, four samples are captured per clock edge at two different thresholds. Two samples are taken at each threshold.)

For probing signals under 2.5Gb/s, you can use the W6601A interposer with the U4164A module's dual clock edge clocking and dual sample mode instead of the quad sample mode. The U4164A module's dual sampling with dual thresholds allows you to capture separate Read and Write samples per clock edge.

#### W6601A Technical Features Summary

- Probes a JEDEC LPDDR4 BGA 200 footprint. Maximum of 10 mm wide X 15 mm long LPDDR4 DRAM package can fit on top of the W6601A interposer without an additional riser or a socket to provide clearance for the RC components.

- For the two flex wings of the interposer, the recommended bend radius is 2.5 mm (0.09") if flex is bent at a rigid portion of the interposer.

- Logic analyzer connections are made using U4208A and U4209A ZIF probe cables. The U4208A/U4209A ZIF connectors doors open on the top of the W6601A wings and away from these wings.

- An isolation Tip Resistor (100 Ohms) and RC components network is present on the W6601A interposer. No RC network present on the U4208A/U4209A probe cables. Also, there are no RCs on the bottom of the interposer.

- Has a power plane and separate ground planes 1.1 V (VDD2/VDDQ) and 1.8 V (VDD1).

#### W6601A Riser

An LPDDR4 BGA 200 ball riser is provided with each W6601A interposer to allow the interposer to clear surrounding devices. Optionally, you can use a Grypper socket. It is not provided with the interposer.

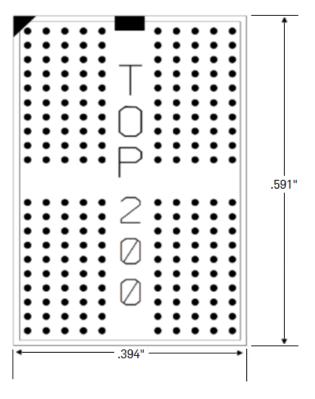

The following figure displays a riser that is provided with the W6601A interposer.

Figure 2 Riser that accompanies the W6601A interposer

NOTE

The LPDDR 200 ball riser includes ground planes for optimal signal integrity. Due to these ground planes, the riser's alignment with the DRAM should be such that the TOP side of the riser must point towards the DRAM and the Pin 1 indicator on the riser must orient towards the "A1" pin of the DRAM.

To know how to solder the riser to the W6601A interposer and PC board, refer to the chapter "W6600A-Series Interposers and Riser Soldering Guidelines" on page 19.

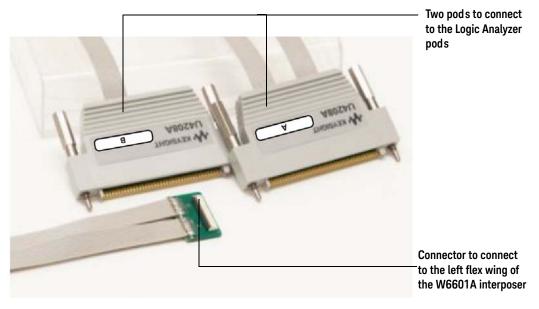

#### U4208A 61-pin ZIF Probe / Cable (for Left Wing)

One U4208A probe cable is required to connect a W6601A interposer's left wing to a U4164A Logic Analyzer module.

Figure 3 U4208A 61-pin ZIF probe cable

To know how to connect a W6601A interposer to a U4208A probe/cable, refer to the following topics in this guide:

• "Connecting the W6601A Interposer to U4208A and U4209A Probe Cables" on page 28

To get information such as its characteristics, specifications, pinout, safety information, accessories, and dimensions of the U4208A probe/cable, refer to the *Keysight U4200A-Series Probes and Cables User Guide* (part number U4200-97000) available on www.keysight.com.

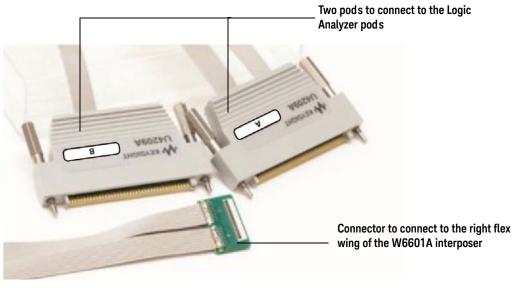

## U4209A 61-pin ZIF Probe / Cable (for Right Wing)

One U4209A probe cable is required to connect a W6601A interposer's right wing to a U4164A Logic Analyzer module.

To know how to connect a W6601A interposer with a U4209A probe/cable, refer to the topic:

• "Connecting the W6601A Interposer to U4208A and U4209A Probe Cables" on page 28

To get information such as its characteristics, specifications, pinout, safety information, accessories, and dimensions of the U4209A probe/cable, refer to the *Keysight U4200A-Series Probes and Cables User Guide* (part number U4200-97000) available on www.keysight.com.

#### Hardware and Software Requirements

Before you start installing the W6600A-series interposers, ensure that you have the following list of hardware and software components needed for these interposers.

| <br>and the second second | Descriptions |  |

|---------------------------|--------------|--|

| rware                     | Requirements |  |

U4164A AXIe-based Logic Analyzer Module

M9502A 2-slot or M9505A 5-slot AXIe chassis to install the U4144A module

M9536A embedded controller or host PC with PCI express adapter card for the chassis

W6600A-series LPDDR4 Interposer(s)

U4208A 61-pin ZIF probe cables to connect the W6601A interposer to Logic Analyzer module One cable needed for each interposer

U4209A 61-pin ZIF probe cables to connect the W6601A interposer to Logic Analyzer module One cable needed for each interposer

| Software Requirements                                                                                     | Licensing                                                            | Description                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic and Protocol Analyzer software version 6.30 or<br>higher.<br>(Required)                             | Unlicensed base software with additional licensing options           | Base software platform for configuring and using Keysight's logic analyzer modules.                                                                                                                                                                                                               |

| B4661A Memory Analysis Software Tools Package version 6.30 or higher. (Required)                          | Includes unlicensed as well as licensed features                     | Base software package that includes configuration files and tools<br>to help you perform DDR/LPDDR post-process as well as<br>real-time protocol compliance violation testing, decode and view<br>memory transactions, and set up your logic analyzer for<br>DDR/LPDDR data capture and analysis. |

| The below-mentioned licensed/unlicensed software fea                                                      | atures from the B4661A software package a                            | are required for W6601A.                                                                                                                                                                                                                                                                          |

| Default LPDDR configuration files<br>(Required)                                                           | Available as an unlicensed standard feature with the B4661A package. | Includes default XML configuration files for use with the W6601A interposer.                                                                                                                                                                                                                      |

| DDR Setup Assistant and DDR Eyefinder software<br>version 6.30 or higher.<br>(Required)                   | Available as an unlicensed standard feature with the B4661A package. | A wizard- like application to help you set up your U4164A logic analyzer properly for use with the W6600A-series interposers.                                                                                                                                                                     |

| DDR Custom Configuration Creator Tool version 6.30<br>or higher<br>(Required)                             | Available as an unlicensed standard feature with the B4661A package. | Allows you to define the footprint layout as per your custom<br>probing solution used in the DDR/LPDDR setup and then create<br>an XML configuration file based on this footprint information.                                                                                                    |

| B4661A-2FP LPDDR Bus Decoder software version<br>6.30 or higher.<br>(Recommended)                         | Available as a licensed feature with the B4661A package              | Allows you to decode and view transactions, commands, and data from a LPDDR1, LPDDR2, LPDDR3 or LPDDR4 SDRAM memory bus in your device under test.                                                                                                                                                |

| B4661A-3FP DDR 2/3/4 Protocol Compliance and<br>Analysis toolset version 6.30 or higher.<br>(Recommended) | Available as a licensed feature with the B4661A package              | <ul> <li>A set of tools to:</li> <li>evaluate and analyze the captured LPDDR data.</li> <li>perform real-time or post process compliance.</li> <li>set up a trigger on the specified address.</li> <li>graphically profile the distribution of memory accesses.</li> </ul>                        |

| B4661A-4FP DDR 2/3/4 Memory Analysis Viewer<br>version 6.30 or higher.<br>(Recommended)                   | Available as a licensed feature with the B4661A package              | <ul> <li>A viewer installed and displayed within the Logic and Protocol<br/>Analyzer GUI to analyze:</li> <li>memory traffic statistics.</li> <li>refresh rate and self-refresh periods.</li> <li>distribution of memory accesses.</li> <li>memory performance measurements.</li> </ul>           |

# NOTE

You can install the above-mentioned software components by downloading the required executables from the Keysight web site at: <a href="http://www.keysight.com/find/lpa-sw-download">www.keysight.com/find/lpa-sw-download</a>.

The following table displays the number of W6600-series interposers and cables required to provide connections to channels of your logic analyzer module.

| DRAM                                                                 | Data Wid th      | Access to                                                                                                                                                                        | Number of Interposers | Number of ZIF Probes                                                | Number of Logic Analyzer<br>Modules |

|----------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------|-------------------------------------|

| LPDDR4 200 ball<br>DRAM used as a<br>single 32-bit<br>channel device | Dual bank 16 bit | <ul> <li>Ck_A</li> <li>All Channel A CA and control signals for Bank 0 and Bank 1</li> <li>All DBI signals</li> <li>Subset of DQS and DQ signals from all byte lanes.</li> </ul> | One W6601A            | One U4208A for the<br>left wing<br>One U4209A for the<br>right wing | One U4164A module                   |

#### Mechanical Considerations

W6601A Interposer Dimensions

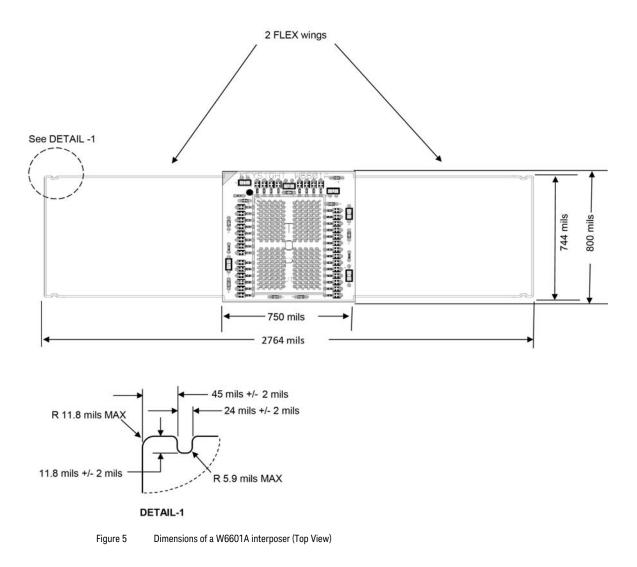

The following figure shows the dimensions of a W6601A LPDDR4 BGA interposer.

W6601A Riser Dimensions

All dimensions are in inches.

.067" thickness

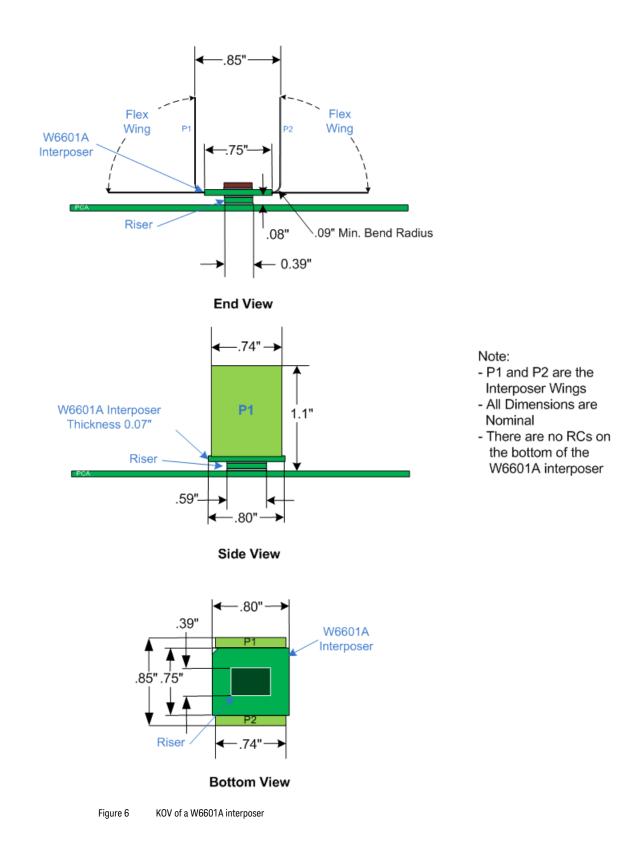

W6601A Keep-Out Volume

# NOTE

You must install the W6601A interposer on a riser (shipped with the interposer) or a grypper socket to provide clearance to surrounding DRAM.

#### 1 Introduction

Keysight W6600A-series LPDDR4 BGA Interposers Installation Guide

2

# W6600A-Series Interposers and Riser Soldering Guidelines

Recommended Soldering Guidelines / 21 Soldering Steps / 22 Interposer Fabrication Notes / 24

In this chapter, Keysight provides the soldering guidelines and information for W6600A-series interposer installation. However, Keysight cannot guarantee the successful interposer installation due to variations in processes and equipment used at individual BGA rework facilities.

Keysight recommends that interposers be installed by companies with specific expertise in this advanced type of processing.

Keysight does not endorse any specific BGA rework facility but recommends using a reputable and experienced BGA rework facility for the installation of BGA interposers. The following links are provided as a convenience to users investigating BGA rework facilities.

| Information on BGA Rework Facilities                                                    |  |

|-----------------------------------------------------------------------------------------|--|

| Circuit Technology Center<br>Haverhill, MA<br>USA                                       |  |

| BGA Rework and Repair Services<br>http://www.circuitrework.com/services/bga.shtml       |  |

| Keysight Technologies Adapter Rework<br>http://www.circuitrework.com/features/671.shtml |  |

| eTech<br>Round Rock, TX<br>www.eTech-WEB.com                                            |  |

| Singularity Electronic Systems                                                          |  |

Singularity Electronic Systems Portsmouth, NH www.singularitysys.com

#### Recommended Reading

BGA Component Rework Procedures http://www.circuitrework.com/guides/9-0.shtml

BGA Component Rework Process Flow http://www.circuitrework.com/guides/9-1-1.shtml

BGA Component Rework Inspection http://www.circuitrework.com/guides/9-1-2.shtml

BGA Component Rework Profile Development, Standard Method http://www.circuitrework.com/guides/9-2-1.shtml

BGA Component Rework Profile Development, Smart Track Method http://www.circuitrework.com/guides/9-2-2.shtml

BGA Component Rework, Eutectic Solder Ball http://www.circuitrework.com/guides/9-3-1.shtml

BGA Component Reballing, Fixture Method http://www.circuitrework.com/guides/9-4-1.shtml

#### **Recommended Soldering Guidelines**

These guidelines are intended for anyone who has decided to install the winged BGA interposers themselves, or would like to provide guidelines to their regular contract manufacturer.

- The W6600A-series interposers are assembled using lead free or leaded soldering processes.

- Observe standard lead-free rework guidelines and processes when applying LPDDR memory devices and attaching a riser to an interposer and DIMM.

- Typical time-above-liquidus (220°C in the case of SAC305 solder) is 30 to 90 seconds with 60 seconds as the good nominal target.

- The peak temperature at the SAC305 solder joints should be a minimum of 235°C.

- It is best to limit the peak temperature on the package of the IC at a maximum of 245°C.

- To minimize heating effects on components mounted on the interposer assembly, a leaded solder process can be used to attach a riser, when it is compatible with your prototype debug and validation methodologies.

- The flex wings on Keysight BGA interposers are made with Pyralux AP, the flex material, and Pyralux FR, the coverlay material with adhesive. Both of these materials have high moisture absorption characteristics, and always require baking prior to processing. Review the DuPont baking recommendation before processing.

- The maximum processing temperature that the W6600A-series interposers can withstand is 260 °C for not more than 90 seconds.

- The W6600A-series interposers are supplied without solder balls. Depending on the exact attachment order, either leaded or lead-free solder may be preferred to attach the interposer to the DUT. The design of the interposer supports either choice.

- The flexible "wings" on the interposer may need to be bent upwards before soldering to avoid mechanical contact with components adjacent to the interposer on the DUT. If interposer wings are bent during the soldering process, precautions must be taken to ensure that the wings do not move during the process. Applying heat to a bent wing has the tendency to cause the wing to relax and this can result in movement during the soldering process that can damage the integrity of the solder joints.

#### Soldering Steps

These steps and guidelines apply only to the proper method of attaching BGA interposers to their target host boards. These do not attempt to provide instructions on how to attach BGA balls to the interposer, nor do these attempt to suggest a flux or a solder paste process.

- 1 Profile Development

- a Profile must conform to the solder paste specification. Use the lowest possible temperatures that will insure reflow.

- *b* Profile must also provide a slow ramp up to temperature.

- c It is recommended that the profile be developed using a non-functional sample interposer in a location on a sample target that is similar to the actual target.

- *d* The highest processing temperature must be in the range of 240 °C to 260 °C. The maximum processing time at the highest temperature must not exceed 90 seconds.

- 2 Material Baking

- a Prior to soldering, bake interposer (to eliminate moisture) for 2-10 hours at 250° F (121° C).

- b Shield flex areas.

- c Polyimide films absorb moisture quickly; therefore, soldering and reflow should be done within 30 minutes after baking.

- *d* A 7 or 9 zone conventional oven is beneficial. A conventional oven is preferred over infra-red.

- Vacuum ovens are also used to remove water. Lower temperatures, such as 150-175 F (65-80 C) can be used. This method also reduces the oxidation of the exposed copper pads.

- *f* After baking, if the units are not reflowed within a few hours, these should be re-baked or placed in a desiccant chamber.

- 3 Heat Shielding

- a Kapton tape is applied to the bottom-side covering the gold contact area and wrapping around the outside edge to the top-side.

- *b* Three layers of Kapton tape are applied to the top-side covering the entire wing extending over to the rigid board.

- c Additional insulating of the wing area is done by applying a thick coating of the high temperature peelable masking to the Kapton tape covering the entire area to reduce the exposure to the hot gas heat cycle.

- 4 Host assembly components must be shielded using Kapton tape, aluminum heat shield blanket, or plates.

- 5 Site Preparation

- a If the interposer is being installed onto a new board with gold pads, these pads should be pre-tin to ensure the pads wet properly, and to lower the chance of oxidation.

- *b* Add solder paste to the target board using a mini-stencil. This is recommended over using flux only.

- 6 Interposer Reflow

- *a* Use the lowest possible temp for reflow Use a slow ramp up to temperature.

- b Aim the shielded wings of the interposer upwards. The minimum bend radius must be 1.27mm (0.05 In) to insure that the copper foil does not fracture.

- c Place the interposer using vision equipped BGA placement/reflow system such as an SRT.

- *d* Reflow per the prepared heating profile.

- 7 Memory placement

- a Add staking epoxy to the four corners of the placed interposer, and cure at 150°C for 2 minutes. This time is defined from the moment the adhesive reaches the cure temperature. As a convenience, the following link has been supplied on a staking adhesive.

#### https://tds.us.henkel.com/NA/UT/HNAUTTDS.nsf/web/7DA17BAB270FA76E882571870000D 6EE/\$File/3609-EN.pdf

- *b* Apply solder paste to the top-side of interposer.

- c Position memory using an SRT (or equivalent) with vision system for manual placement.

- *d* Reflow per the prepared heating profile.

- 8 Post Processing

- a Remove flux residue.

- b Remove any Kapton tape heat shielding and peelable mask material.

- *c* Remove heat shielding from the target board.

#### Interposer Fabrication Notes

#### **Operating Environment**

The W6600A-series interposers are constructed of polyimide material that supports solder attachment of the interposer using the higher temperatures required by a lead-free solder process. The coefficient of thermal expansion for the interposer is 55 ppm/degree C. When operating in a soldered-down environment over a wide range of temperatures, the expansion coefficient of the interposer, DRAM, and system being probed must be matched to avoid stress related failure of the solder connections between the Interposer and attached components. The interposer material allows operation over an industrial temperature range of -40 to +85 degrees Celsius (non-condensing), subject to the above constraint.

#### **Mechanical Dimensions**

When a W6600A-series interposer is soldered to a riser, flatness must be maintained on the order of 3.5 mils or less across the BGA footprint to maximize successful soldering to the interposer.

Keysight W6600A-series LPDDR4 BGA Interposers Installation Guide

# 3

# Setting up the W6601A Interposer

W6601A Interposer Setup - Overview / 26 Soldering the W6601A Interposer / 27 Connecting the W6601A Interposer to U4208A and U4209A Probe Cables / 28 Connecting the U4208A and U4209A Probe Cables to a U4164A Logic Analyzer / 31

# W6601A Interposer Setup - Overview

|         | 1 | Solder the interposer, riser, and memory components. (See page 27)                                                                                                               |

|---------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 2 | Connect the interposer flex wings to U4208A and U4209A probe cables. (See page 28)                                                                                               |

|         | 3 | Connect the U4208A and U4209A probe cables to a U4164A Logic Analyzer module's pods. (See page 31)                                                                               |

| CAUTION |   | Use ESD precautions. Electrostatic discharge can damage components on your board or in the interposer. Use a grounded wrist strap and other ESD control measures as appropriate. |

| NOTE    |   | Do not open the vacuum sealed packs of the W6601A interposer until you are ready to install the interposer. Discard these packs once the package is opened.                      |

#### Soldering the W6601A Interposer

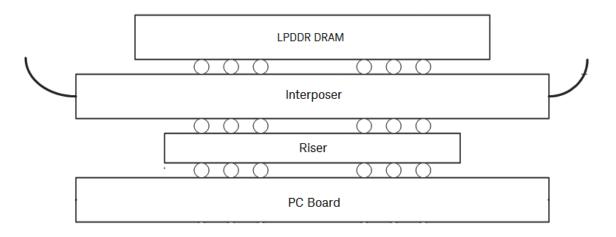

The W6601A interposer needs to be attached to the JEDEC LPDDR4 BGA 200 footprint on the design to be probed. The desired DRAM is soldered to the top side of the interposer. This attachment may occur in any order (i.e. first solder the interposer to the DUT, and then solder the DRAM to the interposer, or first solder the DRAM to the interposer, and then solder the DRAM+interposer assembly to the DUT). The interposer is designed to tolerate lead-free soldering temperature profiles. However, it is always recommended to apply the minimum temperature required and the minimum number of heating/cooling cycles to reduce risk of any damage to the interposer.

The stack up of these soldered components is illustrated in the following figure.

Figure 7 PC board, riser, interposer, and DRAM stack up

## NOTE

A maximum of 10 mm wide X 15 mm long LPDDR4 DRAM package can fit on top of the W6601A interposer without an additional riser or a socket between the DRAM and interposer to provide clearance for the RC components.

Refer to the chapter "W6600A-Series Interposers and Riser Soldering Guidelines" on page 19.

#### Connecting the W6601A Interposer to U4208A and U4209A Probe Cables

After soldering components, you can start connecting the W6601A interposer to the U4208A and U4209A probe cables.

# CAUTION

Please handle the interposer with care and ensure that the wings on the W6601A interposer are properly latched to the ZIF connectors on the U4208A and U4209A probe cables.

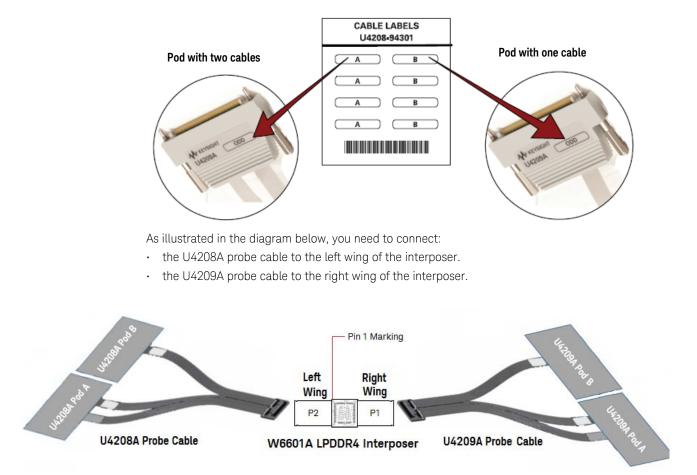

U4208A and U4209A cables ship with pod labels unattached. Use the sheet of labels included with the cable shipment to label pods as follows.

Figure 8 W6601A Interposer and U4208A / U4209A Probe Cable Connections

The door on the ZIF connector of the U4208A/U4209A cable closes against the top of the ZIF wing of the interposer.

To attach a U4208A or a U4209A ZIF connector to a flex wing of the W6601A interposer, perform the following three steps.

- 1 Angle the flex wing of the interposer into the probe cable's ZIF connector.

- 2 Align the probe cable's ZIF connector tabs with interposer's wing notches.

- 3 Shut the ZIF door.

#### W6601A Interposer Wings Pinout

The table on the next page lists the pinout of the two wings of a W6601A interposer. The table includes the signals being probed when using the interposer in a dual sampling mode or a quad sampling mode (supported by the U4164A logic analyzer module).

In this table,

- Clock/Qualifier inputs are highlighted with yellow

- Signals that can be quad-sampled are highlighted with green

- Single-sampled signals are highlighted with blue

- Table cells marked with \_\_\_\_\_\_ indicate pins that are not accessible.

|     | W6601A Inter | poser Wings |

|-----|--------------|-------------|

| Pin | Right Wing   | Left Wing   |

| 2   | DQ8_A        | DQ0_B       |

| 4   | DQ9_A        |             |

| 6   | DMI1_A       | DQ7_B       |

| 8   | DQ15_A       |             |

| 10  | CKc_A        | $\geq$      |

| 12  | CKt_A        | $\geq$      |

| 14  | CA2_A        | DMI0_B      |

| 16  | CA3_A        |             |

| 18  | CA4_A        | DQ1_B       |

| 20  | CA5_A        |             |

| 22  |              | DQ2_B       |

| 24  |              |             |

| 26  |              | DQ4_B       |

| 28  | DQ12_B       |             |

| 30  | GND          | CKE1_A      |

| 32  | RESET_N      | GND         |

| 34  |              | DQ3_B       |

| 36  | DQ11_B       |             |

| 38  |              | CS1_A       |

| 40  | DQ10_B       |             |

| 42  |              | CS0_A       |

| 44  | DQ9_B        | CA1_A       |

| 46  |              | CA0_A       |

| 48  | DMI1_B       | ODT_CA_A    |

| 50  | $\geq$       | CKEO_A      |

| 52  | $\geq$       | GND         |

| 54  |              | DQ7_A       |

| 56  | DQ15_B       | DMI0_A      |

| 58  |              | DQS0t_A     |

| 60  | DQ8_B        | DQ0_A       |

| Pin | U4209A       | U4208A      |

Table 1 W6601A Interposer Wings Pinout

#### Connecting the U4208A and U4209A Probe Cables to a U4164A Logic Analyzer

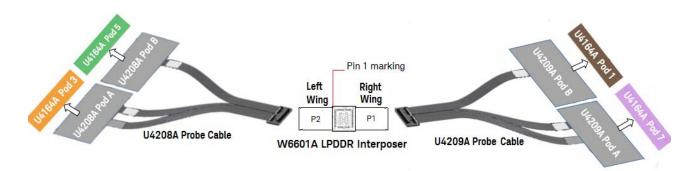

In a W6601A interposer setup, you connect the U4208A and U4209A probe cable pods to U4164A logic analyzer pods as per the mapping shown in the table below.

| Probe Cable Pods  | U4164A Logic Analyzer<br>Pods |

|-------------------|-------------------------------|

| U4209A Cable Pods |                               |

| Pod A             | Pod 7                         |

| Pod B             | Pod 1                         |

| U4208A Cable Pods |                               |

| Pod A             | Pod 3                         |

| Pod B             | Pod 5                         |

#### NOTE

In a dual-sampled setup, the U4164A logic analyzer samples data twice per clock edge. Two thresholds are used with one sample taken per threshold. For LPDDR systems running less than 2.5GHz, the dual sampling allows separate thresholds and separate sample positions to be specified for DDR Reads and Writes.

In a quad-sampled setup, four samples are taken per clock edge. Two thresholds are used with two samples taken per threshold.

The mapping of the U4208A and U4209A probe cable pods and logic analyzer pods is also illustrated with the help of the following diagram.

Figure 9 Connections between U4208A and U4209A probe cables and Logic Analyzer pods

Logic Analyzer Channels to Signals Mapping

When you connect the U4208A and U4209A probe cables to a U4164A Logic Analyzer as per the connection diagram in Figure 9, the logic analyzer channels are mapped to DDR4 signals as per the table displayed below.

These signals are automatically configured when you load one of the configuration files supplied with the Keysight B4661A LPDDR decoder software.

#### Notes:

- Clock inputs for each logic analyzer pod are highlighted with yellow in this table.

- Table cells marked with \_\_\_\_\_\_ indicate logic analyzer channels that are not accessible.

Table 2 Signals and Logic Analyzer Channels Mapping when using the W6601A Interposer

| Logic Analyzer Pod<br>and its Channels |      | Signals on<br>U4208A probe<br>cable Pod A |       | Analyzer Pod<br>ts Channel s | Signals on<br>U4208A probe<br>cable Pod B |

|----------------------------------------|------|-------------------------------------------|-------|------------------------------|-------------------------------------------|

|                                        | 0    | DQ0_B                                     |       | 0                            | CS0_A                                     |

|                                        | 1    |                                           |       | 1                            | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|                                        | 2    | DQ7_B                                     |       | 2                            | CA1_A                                     |

|                                        | 3    |                                           |       | 3                            | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |

|                                        | 4    | DMI0_B                                    |       | 4                            | CA0_A                                     |

|                                        | 5    |                                           |       | 5                            | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|                                        | 6    | DQ1_B                                     |       | 6                            | ODT_CA_A                                  |

| Pod 3                                  | 7    |                                           | Pod 5 | 7                            | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|                                        | 8    | DQ2_B                                     |       | 8                            | DQ7_A                                     |

|                                        | 9    |                                           |       | 9                            | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |

|                                        | 10   | DQ4_B                                     |       | 10                           | DMI0_A                                    |

|                                        | 11   |                                           |       | 11                           | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|                                        | 12   | DQ3_B                                     |       | 12                           | DQS0t_A                                   |

|                                        | 13   |                                           |       | 13                           | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|                                        | 14   | CS1_A                                     |       | 14                           | DQ0_A                                     |

|                                        | 15   |                                           |       | 15                           | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |

|                                        | CLK  | CKE1_A                                    |       | CLK                          | CKE0_A                                    |

|                                        | CLK# | GND                                       |       | CLK#                         | GND                                       |

|       | nalyzer Pod<br>s Channel s | Signals on<br>U4209A probe<br>cable Pod A |       | yic Analyzer Pod<br>nd its Channels | Signals on<br>U4209A probe<br>cable Pod B   |

|-------|----------------------------|-------------------------------------------|-------|-------------------------------------|---------------------------------------------|

|       | 0                          | DQ8_B                                     |       | 0                                   | CA5_A                                       |

|       | 1                          |                                           |       | 1                                   | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |

|       | 2                          | DQ15_B                                    |       | 2                                   | CA4_A                                       |

|       | 3                          |                                           |       | 3                                   | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|       | 4                          | DMI1_B                                    |       | 4                                   | CA3_A                                       |

|       | 5                          |                                           |       | 5                                   | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|       | 6                          | DQ9_B                                     |       | 6                                   | CA2_A                                       |

| Pod 7 | 7                          |                                           | Pod 1 | 7                                   | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|       | 8                          | DQ10_B                                    |       | 8                                   | DQ15_A                                      |

|       | 9                          |                                           |       | 9                                   | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$     |

|       | 10                         | DQ11_B                                    |       | 10                                  | DMI1_A                                      |

|       | 11                         |                                           |       | 11                                  | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|       | 12                         | DQ12_B                                    |       | 12                                  | DQ9_A                                       |

|       | 13                         |                                           |       | 13                                  | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |

|       | 14                         |                                           |       | 14                                  | DQ8_A                                       |

|       | 15                         |                                           |       | 15                                  | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$   |

|       | CLK                        | RESET_N                                   |       | CLK                                 | CKt_A                                       |

|       | CLK#                       | GND                                       |       | CLK#                                | CKc_A                                       |

Signals not probed by the Logic Analyzer

The following signals are omitted from the Logic Analyzer connections for the W6601A interposer.

#### 3 Setting up the W4641A Interposer

| Interposer | Signal Name |

|------------|-------------|

| W6601A     | DNU         |

|            | VDDQ        |

|            | VDD1        |

|            | VDD2        |

|            | ODT_CA_B    |

|            | CAO_B       |

|            | CA1_B       |

|            | DQ3_A       |

|            | DQ2_A       |

|            | DQ1_A       |

|            | DQS0c_A     |

|            | CS1_B       |

|            | DQS0c_B     |

|            | DQS0t_B     |

|            | DQ6_B       |

|            | DQ5_B       |

|            | CS0_B       |

|            | CKE0_B      |

|            | DQ4_A       |

|            | DQ5_A       |

|            | DQ6_A       |

|            | ZQO         |

|            | CS2_B       |

|            | CKE1_B      |

|            | ZQ1         |

|            | CKE2_A      |

|            | CKE2_B      |

|            | CKt_B       |

|            | DQ14_B      |

|            | DQ13_b      |

|            | CA2_B       |

|            | CKc_B       |

|            | DQ12_A      |

|            | DQ13_A      |

|            | DQ14_A      |

|            | DQS1t_A     |

|            | DQS1c_A     |

|            | CA3_B       |

|            | DQS1c_B     |

|            | DQS1t_B     |

|            | CA4_B       |

|            | CA5_B       |

|            | ZQ2         |

|            | DQ11_A      |

|            | DQ10_A      |

Keysight W6600A-series LPDDR4 BGA Interposers Installation Guide

# 4 Setting Up the Logic Analyzer for W6600A-series Interposers

Before You Start / 36 Loading a Configuration File / 37

#### Before You Start

Ensure that all the software components listed in the topic "Hardware and Software Requirements" on page 13 are installed on the host computer and the required software licenses are also obtained and installed.

#### Loading a Configuration File

When you install the Keysight B4661A Memory Analysis software package, a set of XML LPDDR configuration files is installed as a part of the standard unlicensed features of this package. Based on the software configuration (see page 9) in which you want to use your W6601A interposer with the logic analyzer, you can load an appropriate configuration file from this set in the Logic and Protocol analyzer GUI.

Licensing is not required for obtaining or loading these configuration files.

When you load a configuration file, it will set up the buses and signals, add the LPDDR decoder tool, and add a listing tool in the Logic and Protocol Analyzer GUI. The LPDDR Decoder tool is a licensed feature of the B4661A software package.

To load a provided configuration file:

- 1 Close the logic analyzer GUI window, if it is open.

- 2 Navigate to the following folder that contains all the LPDDR configuration files. Users/Public/Public Documents/Keysight Technologies/Logic Analyzer/Default Configs/Keysight/LPDDR **Bus Decoder**

- 3 Select the LPDDR bus type.

- 4 Select the **BGA** and then choose a configuration file corresponding to the bus size and speed.

- 5 Double-click the configuration file to open it.

When you click on a configuration file, the Logic and Protocol Analyzer software will start and configure itself to use the decoder.

The logic analyzer Buses/Signals setup dialog allows you to assign descriptive labels to each analyzer channel that associate each channel with the particular DRAM and DRAM signal being probed.

#### NOTE

If your unique multi-DRAM configuration is not covered by one of the default configurations, you can use the *DDR Custom Configuration Creator* tool installed with the B4661A Memory Analysis SW package to create your own custom LPDDR BGA configuration.

#### NOTE

It is recommended that you use the Advanced Probe Settings (APS) for all signals on all W6600A-series interposers. For instructions, refer to the application note "*Capture Highest* DDR3 Data rates using Advanced Probe Settings" available at: http://literature.cdn.keysight.com/litweb/pdf/5991-0799EN.pdf?id=2284314.

To save a configuration file

After you set up the logic analyzer, it is strongly recommended that you save the configuration.

To save your work, select File>Save As... and save the configuration as an ALA format file.

ALA format configuration files are more complete and efficient than XML format configuration files. See the Logic and Protocol Analyzer online help for more information on these formats.

4 Setting Up the Logic Analyzer for W6600A-Series Interposers

Keysight W6600A-series LPDDR4 BGA Interposers Installation Guide

5

# Characteristics, Regulatory, Safety and Storage Information

Operating Characteristics / 40 Storage, Inspection, Baking, and Cleaning Guidelines / 41 Regulatory Notices / 42

## **Operating Characteristics**

The following operating characteristics are not specifications, but are typical operating characteristics.

| Characteristics                          | Description                                                                                                                                                             |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature                              | Operating: +5° C to +40° C<br>Non Operating : - 40 ° C to +70° C                                                                                                        |

| Altitude                                 | 4,600 m (15,000 ft)                                                                                                                                                     |

| Relative Humidity Range<br>Noncondensing | 50% RH Min/80% RH Max at 40° C noncondensing.<br>Avoid sudden, extreme temperature changes which could cause condensation on the circuit<br>board. For indoor use only. |

| Characteristics | Description                                                                  |

|-----------------|------------------------------------------------------------------------------|

| To interposer   | Memory bus signals from target system                                        |

| From interposer | High-density connectors for Keysight U4164A AXIe-based logic analyzer module |

#### Storage, Inspection, Baking, and Cleaning Guidelines

The following are some of the guidelines for storing, shelf life, and cleaning of the W6600A-series interposers.

Guidelines for Shelf Life and Solder-ability of W6600A-series Interposers

If your Interposer exceeds shelf life (1 year) before solder into application, use the following inspection and baking method.

- Inspect the humidity indicator within moisture proof vacuum sealed bag(s).

- If the humidity indicator shows moisture then bake the board at 120 degrees C for 4 hours and perform the solder-ability test.

- If the test passes, proceed with the assembly (reflow) of interposer.

- If delamination occurs, the interposer cannot be used.

Cleaning of W6600A-series Interposer Gold Fingers

- Use Isopropyl alcohol to clean interposer contacts.

- Never use abrasive cleaning materials.

## **Regulatory Notices**

WEEE Compliance

|            | Safety Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |               | This product complies with the WEEE Directive (2002/96/EC) marking requirements. The affixed label indicates that you must not discard this electrical/electronic product in domestic household waste. <i>Product Category: With reference to the equipment types in the WEEE Directive Annex I, this product is classed as a "Monitoring and Control Instrumentation" product.</i> <b>Do not dispose in domestic household waste. To return unwanted products, contact your local Keysight office, or see "www.keysight.com"</b> for more information. |

| China RoHS |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | W6601A        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 40            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Index

#### В

B4661A, **37** B4661A-1FP, B4661A-3FP, B4661A-4FP, bake, **41** bend radius,

## С

cable connections, 28 characteristics, 39 China RoHS, 42 cleaning, interposer, 41 configuration files, 37 configuration files, saving, 37

## D

DDR Custom Configuration Creator Tool, 13 DDR Eyefinder, 13 DDR Setup Assistant, 13 dimensions, W6601A interposer, 15 DRAM package, 10

# Е

equipment required, 13

# Н

humidity indicator, 41

# I

in this guide, 3 installing the W6601A interposer, 25 interposer, inputs to, 40 interposer, outputs from, 40 introduction, 7

## Κ

KOV, 16

#### L

logic analysis system set up, 35 logic analyzer channel mapping, 31 logic analyzer connections, 31 LPDDR configuration files, 13, 37

#### Μ

mechanical considerations, 15

# 0

operating characteristics, 40

#### Ρ

pinout, 29

# R

regulatory information, regulatory notices, required probes, cables, LA modules, **14** rework facilities, riser, **10**, **16**,

# S

safety information, 39 shelf life, 41 signals not probed, 33 soldering guidelines, 19 soldering processes, 21 soldering temperature, 21 storage guidelines, 41

## U

U4208A, 11, 12

#### W

W6601A, 9 W6601A channel mapping, 32 W6601A feature summary, 10 W6601A KOV, 16 WEEE compliance, 42 Index

www.keysight.com